#### **Edith Cowan University**

#### **Research Online**

Theses: Doctorates and Masters

**Theses**

1-1-2004

## CMOS digital pixel sensor array with time domain analogue to digital conversion

Alistair J. Kitchen Edith Cowan University

Follow this and additional works at: https://ro.ecu.edu.au/theses

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Kitchen, A. J. (2004). CMOS digital pixel sensor array with time domain analogue to digital conversion. Edith Cowan University. Retrieved from https://ro.ecu.edu.au/theses/765

This Thesis is posted at Research Online. https://ro.ecu.edu.au/theses/765

# **Edith Cowan University Research Online**

Theses: Doctorates and Masters

Theses

2004

# CMOS digital pixel sensor array with time domain analogue to digital conversion

Alistair J. Kitchen *Edith Cowan University*

#### Recommended Citation

$Kitchen, A.\,J.\,(2004).\,CMOS\,digital\,pixel\,sensor\,array\,with\,time\,domain\,analogue\,to\,digital\,conversion.\,Retrieved\,from\,http://ro.ecu.edu.au/theses/765$

This Thesis is posted at Research Online. http://ro.ecu.edu.au/theses/765

# Edith Cowan University Copyright Warning

You may print or download ONE copy of this document for the purpose of your own research or study.

The University does not authorize you to copy, communicate or otherwise make available electronically to any other person any copyright material contained on this site.

You are reminded of the following:

- Copyright owners are entitled to take legal action against persons who infringe their copyright.

- A reproduction of material that is protected by copyright may be a copyright infringement. Where the reproduction of such material is done without attribution of authorship, with false attribution of authorship or the authorship is treated in a derogatory manner, this may be a breach of the author's moral rights contained in Part IX of the Copyright Act 1968 (Cth).

- Courts have the power to impose a wide range of civil and criminal sanctions for infringement of copyright, infringement of moral rights and other offences under the Copyright Act 1968 (Cth).

Higher penalties may apply, and higher damages may be awarded, for offences and infringements involving the conversion of material into digital or electronic form.

#### CMOS DIGITAL PIXEL SENSOR ARRAY WITH TIME DOMAIN ANALOGUE TO DIGITAL CONVERSION

By

Alistair J. Kitchen

A thesis submitted for the degree of Master of Engineering Science

aŧ

School of Engineering and Mathematics

Edith Cowan University

Principal Supervisor : Assoc. Prof. Abdessalam Bouzerdoum

Co-Supervisor : Dr Amine Bermak

## **USE OF THESIS**

| <b>-</b> |               | <b>T</b> |           | •      |                           |          |                 |                                         |

|----------|---------------|----------|-----------|--------|---------------------------|----------|-----------------|-----------------------------------------|

| INDI     | ICA At        | Indeie   | ctatamant | IC DO  | HADHINAN                  | in thic  | VARSIAN         | of the thesis.                          |

| 1115     | <b>55 0</b> 1 | 1110010  | Statement | 13 110 | ı II ICIUU <del>C</del> U | าทา นาเจ | <b>VCISIOII</b> | UI III II |

#### DECLARATION

I certify that this thesis does not incorporate without acknowledgement any material previously submitted for a degree or diploma in any institution of higher education; and that to the best of my knowledge and belief it does not contain any material previously published or written by another person except where due reference is made in the text.

# **Publications**

A  $64 \times 64$  CMOS digital pixel array based on pulse width analogue to digital conversion, with on chip linearising circuit. *Proceedings of SPIE*, volume 5274, December 2003.

Time domain analogue to digital conversion in a digital pixel sensor array. Proceedings of IEEE, International Workshop on Electronic Design, Test and Applications, January 2004.

# Acknowledgements

I wish to express my gratitude to Dr Amine Bermak for giving me the opportunity to work on this project, and to his wife and family for their kindness.

I would also like to thank Associate Professor Abdessalam Bouzerdoum for his encouragement and patience, and for being so generous with his time.

## Abstract

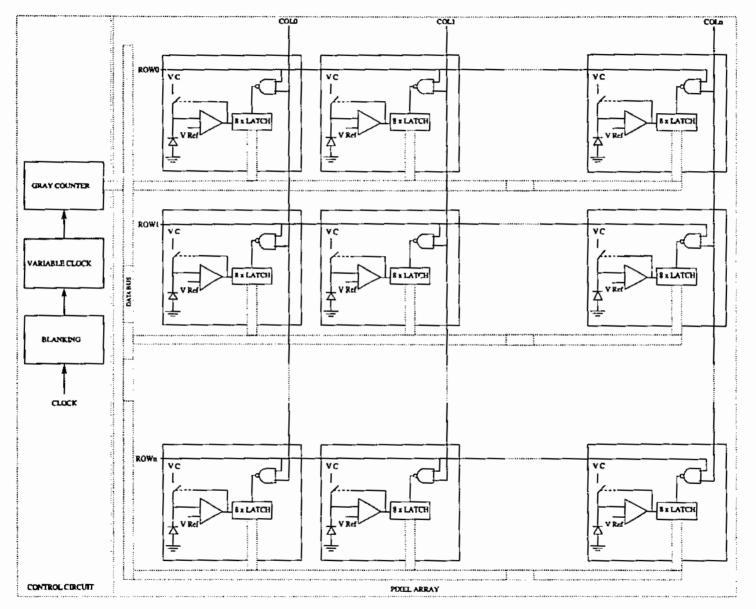

This thesis presents a digital pixel sensor array, which is the first stage of an ongoing project to produce a CMOS image sensor with on-chip image processing. The analogue to digital conversion is performed at the pixel level, with the result stored in pixel memory. This architecture allows fast, reliable access to the image data and simplifies the integration of the image array and the processing logic.

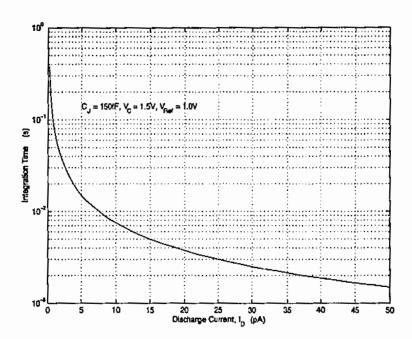

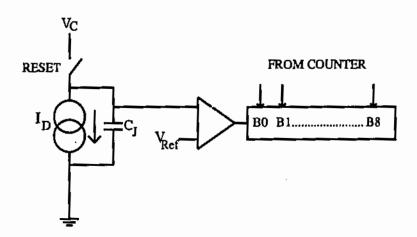

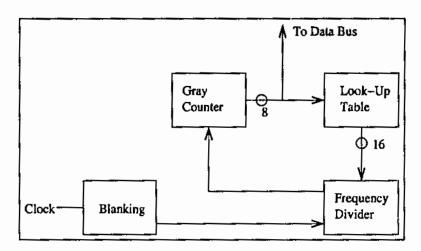

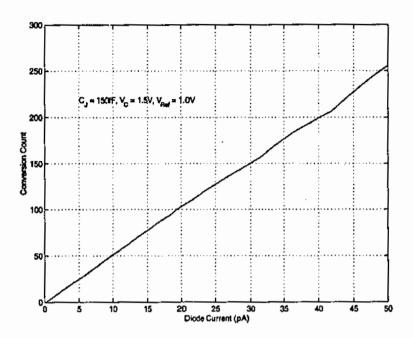

Each pixel contains a photodiode sensor, a comparator, memory and addressing logic. The photodiode sensor operates in integrating mode, where the photodiode junction capacitance is first charged to an initial voltage, and then discharged by the photodiode leakage current, which is comprised mainly of optically generated carriers. The analogue to digital conversion is performed by measuring the time taken for the photodiode cathode voltage to fall from its initial voltage, to the comparator reference voltage. This triggers the 8-bit pixel memory, which stores a data value representative of the time. The trigger signal also resets the photodiode, which conserves the charge stored in the junction capacitance, and also prevents blooming. An on-chip control circuit generates the digital data that is distributed globally to the array. The control circuit compensates for the inverse relationship between the integration time and the photocurrent by adjusting the data clock timing. The period of the data clock is increased at the same rate as the integration time, resulting in a linear relationship between the digital data and the photocurrent.

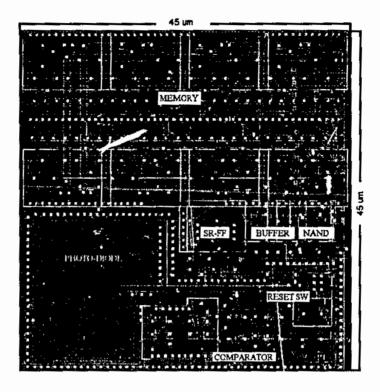

The design is realised as a  $64 \times 64$  pixel array, manufactured in  $0.35\mu m$  3.3 V CMOS technology. Each pixel occupies an area of  $45\mu m \times 45\mu m$  with a 12.3% fill factor, and the entire pixel array and control circuit measures 3.7mm  $\times$  3.9mm.

Experimental results confirm the operation of the digital pixel, and the linearising control circuit. The digital pixel has a dynamic range of 85dB, and can be adapted to different lighting conditions by varying a single clock frequency. The data captured by the array can be randomly accessed, and is read from the array nondestructively.

# Contents

| Publications |       | ations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A            | ckno  | vledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A            | bstra | to a second of the first of the |

| 1            | Inti  | oduction Thesis Objections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              | 1.1   | Thesis Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | 1.2   | Thesis Organisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2            | Rev   | iew of Digital Image Sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | 2.1   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | 2.2   | Charge Coupled Device Sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              | 2.3   | Passive and Active CMOS Sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              |       | 2.3.1 Analogue to Digital Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |       | 2.3.2 Fixed Pattern Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|              |       | 2.3.3 Temporal Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              |       | 2.3.4 Fill Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | •     | 2.3.5 Spatial Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | 2.4   | Digital Pixel Sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              |       | 2.4.1 Near Sensor Image Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              |       | 2.4.2 DPS Architecture Review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              | 2.5   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3            | Tin   | e Domain Analogue to Digital Conversion 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|              | 3.1   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | 3.2   | CMOS Image Sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | 3.3   | Photodiode Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 3.4  | Time Domain Analogue to Digital Conversion   | 20         |

|---|------|----------------------------------------------|------------|

|   |      | 3.4.1 Primary Clock Frequency                | 21         |

|   |      | 3.4.2 Minimum Integration Time Offset        | 22         |

|   |      | 3.4.3 Linear Conversion                      | <b>2</b> 3 |

|   | 3.5  | Conversion Error Analysis                    | 30         |

|   | 3.6  | Data Encoding                                | 34         |

|   | 3.7  | Conclusion                                   | 36         |

| 4 | VLS  | I Implementation                             | 38         |

|   | 4.1  | Introduction                                 | 38         |

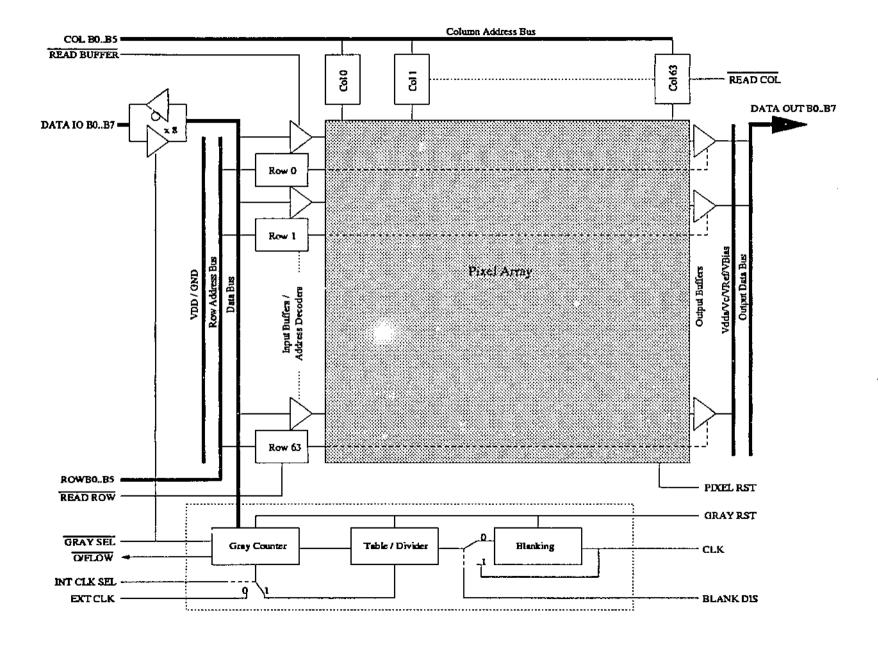

|   | 4.2  | Array Architecture                           | 38         |

|   | 4.3  | Pixel Architecture                           | 40         |

|   | 4.4  | On-Pixel Analogue Circuit                    | 42         |

|   |      | 4.4.1 Photodiode and Photocurrent Estimation | 43         |

|   |      | 4.4.2 Analogue Comparator                    | 43         |

|   |      | 4.4.3 SR Latch                               | 46         |

|   |      | 4.4.4 Reset Switch                           | 47         |

|   | 4.5  | On Pixel Digital Circuit                     | 48         |

|   |      | 4.5.1 Buffers                                | 48         |

|   |      | 4.5.2 Memory                                 | 49         |

|   |      | 4.5.3 Column/Row Decoder                     | 50         |

|   | 4.6  | Pixel Simulation                             | 51         |

|   | 4.7  | Control Circuit                              | 51         |

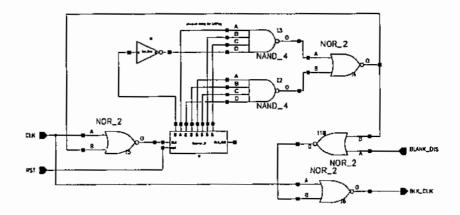

|   |      | 4.7.1 Blanking Circuit                       | 54         |

|   |      | 4.7.2 Gray Counter                           | 55         |

|   |      | 4.7.3 Lookup Table                           | 55         |

|   |      | 4.7.4 Frequency Divider                      | 56         |

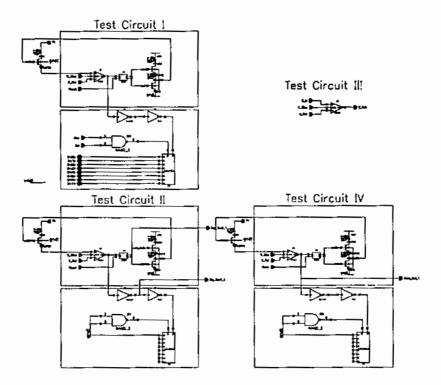

|   |      | 4.7.5 Test Selection Circuits                | 56         |

|   | 4.8  | Control Circuit Simulation                   | 56         |

|   | 4.9  | System Simulation                            | 57         |

|   | 4.10 | Floor-planning and Layout                    | 60         |

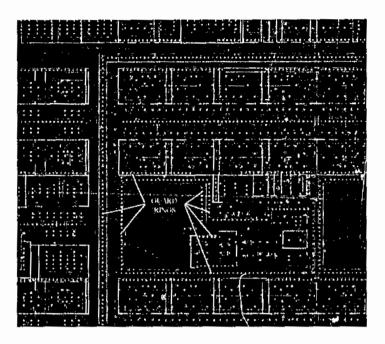

|   |      | 4.10.1 Substrate Coupling                    | 61         |

|   |      | 4.10.2 Device Matching                       | 62         |

|   | 411  | Complusion                                   | e A        |

| 5 | Ope  | ration  | and Testing of the DPS Array | 65   |

|---|------|---------|------------------------------|------|

|   | 5.1  | Introd  | uction                       | . 65 |

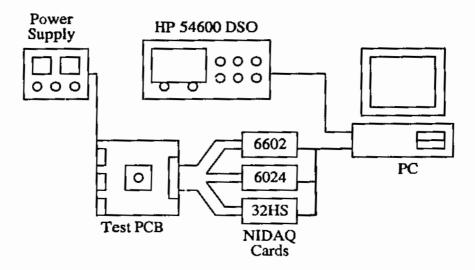

|   | 5.2  | Test E  | Environment                  | . 66 |

|   |      | 5.2.1   | Electrical Test Equipment    | . 66 |

|   |      | 5.2.2   | Optical Test Equipment       | . 68 |

|   | 5.3  | Image   | Capture Operation            | . 68 |

|   |      | 5.3.1   | Exposure Phase               | . 70 |

|   |      | 5.3.2   | Read Phase                   | . 71 |

|   | 5.4  | Contro  | ol Circuit Test Strategies   | . 71 |

|   | 5.5  | Pixel ' | Test Structures              | . 73 |

|   | 5.6  | Contro  | ol Circuit Testing           | . 74 |

|   | 5.7  | Digita  | l Pixel Sensor Testing       | . 75 |

|   |      | 5.7.1   | Test Circuit Signals         | . 76 |

|   |      | 5.7.2   | Conversion Linearity         | . 76 |

|   |      | 5.7.3   | Dark Current                 | . 78 |

|   |      | 5.7.4   | Primary Clock Frequency      | . 79 |

|   | 5.8  | DPS A   | Array Testing                | . 80 |

|   |      | 5.8.1   | Image Capture                | . 81 |

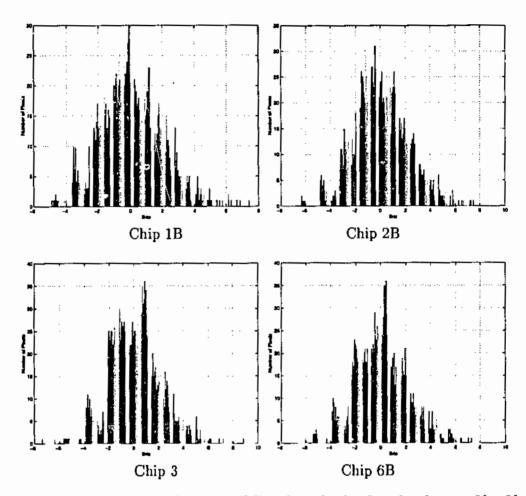

|   |      | 5.8.2   | Fixed Pattern Noise          | . 82 |

|   |      | 5.8.3   | Adaptation                   | . 84 |

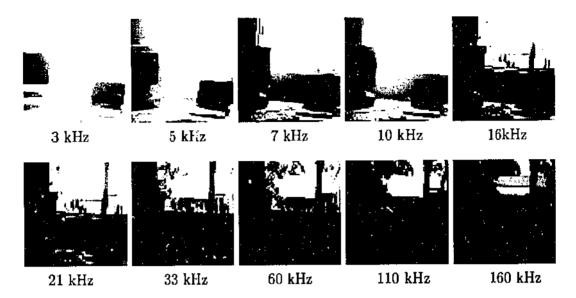

|   |      | 5.8.4   | Spectral Response            | . 86 |

|   |      | 5.8.5   | Array Power Consumption      | . 87 |

|   | 5.9  | Discus  | sion , , . , ,               | . 91 |

|   | 5.10 | Conclu  | ısion                        | . 92 |

| 6 | Con  | olunia  | n and Further Work           | 93   |

| U | 6.1  |         | Summary                      | -    |

|   | 6.2  |         | er Work                      |      |

|   | 6.3  |         | g Remarks                    |      |

|   | ប.ស  | Otostu  | g Remarks                    | . 30 |

| A | Loo  | kup Te  | able Entries                 | 96   |

| В | Pin  | List    |                              | 97   |

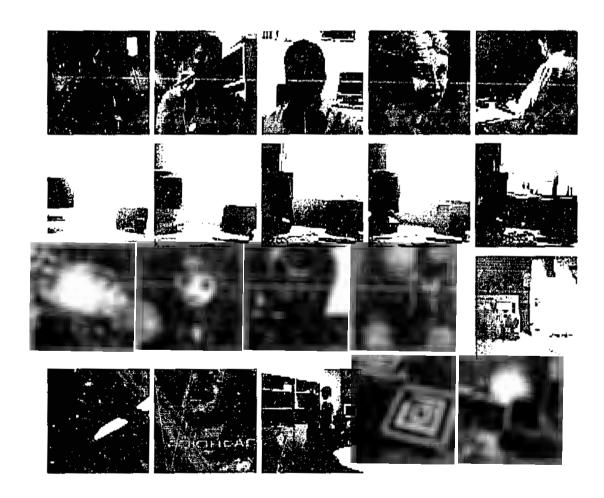

| C | Sam  | ole In  | 18ges                        | 100  |

# List of Figures

| 2.1  | Simplified CCD structure                                             | 6  |

|------|----------------------------------------------------------------------|----|

| 2.2  | Passive and active pixel sensor schematics                           | 7  |

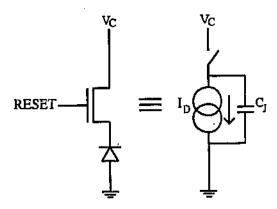

| 3.1  | Photodiode and equivalent circuit                                    | 19 |

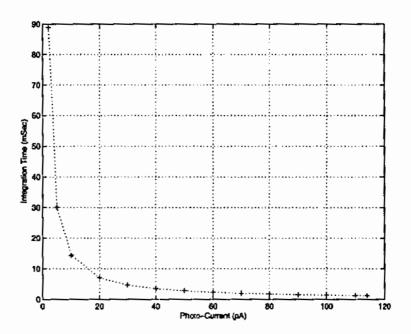

| 3.2  | Integration time versus photocurrent                                 | 20 |

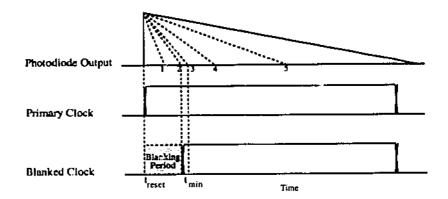

| 3.3  | Integration time and blanking period timing diagram                  | 22 |

| 3.4  | Simulation input image, River.bmp                                    | 24 |

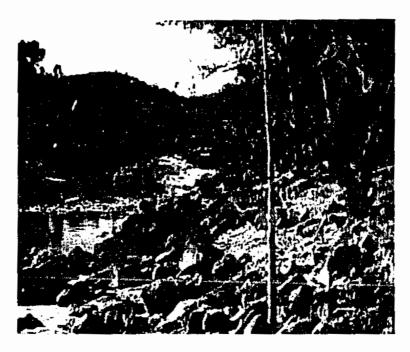

| 3.5  | Simulated image conversion, without blanking, fixed clock            | 26 |

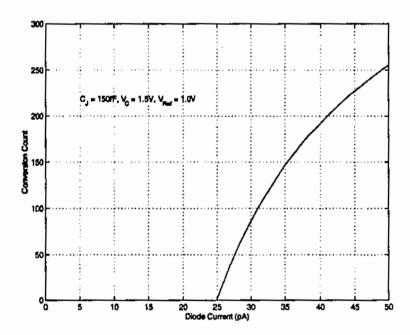

| 3.6  | Conversion count versus photocurrent, without blanking, fixed clock. | 26 |

| 3.7  | Simulated image conversion, with blanking, fixed clock               | 27 |

| 3.8  | Conversion count versus photocurrent, with blanking, fixed clock     | 27 |

| 3.9  | Simulated image conversion, with blanking, variable clock frequency  | 29 |

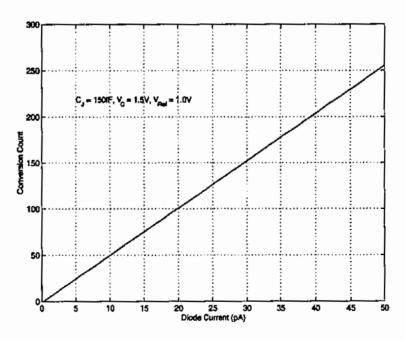

| 3.10 | Conversion count versus photocurrent, with blanking, variable clock  |    |

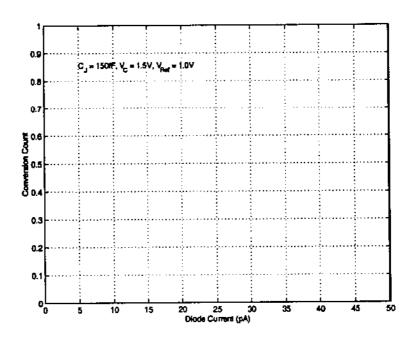

|      | frequency.                                                           | 29 |

| 3.11 | Pixel architecture                                                   | 30 |

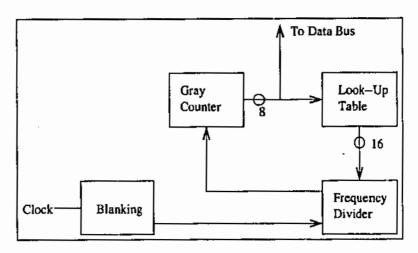

| 3.12 | Control circuit block diagram                                        | 31 |

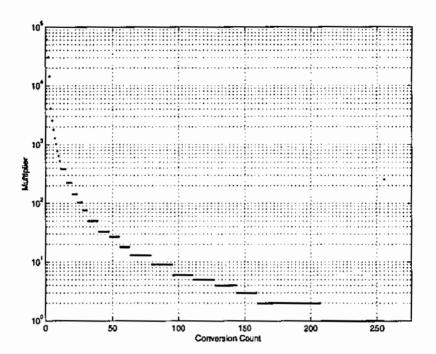

| 3.13 | Conversion count versus photocurrent using approximated multiplier   |    |

|      | values                                                               | 35 |

| 3.14 | Nonlinearity error, using approximated multiplier values             | 35 |

| 4.1  | Proposed DPS array architecture                                      | 39 |

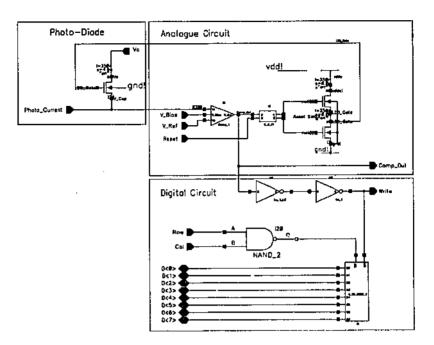

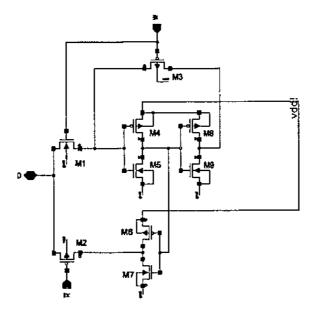

| 4.2  | Pixel schematic                                                      | 42 |

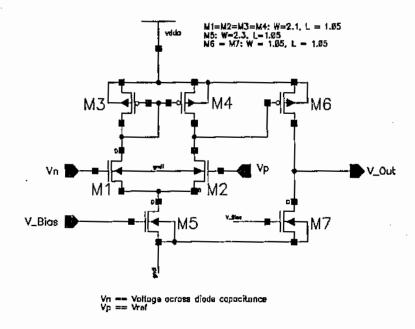

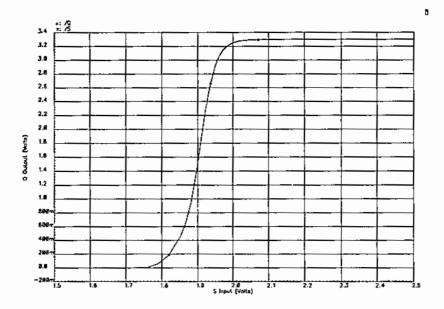

| 4.3  | Comparator schematic                                                 | 44 |

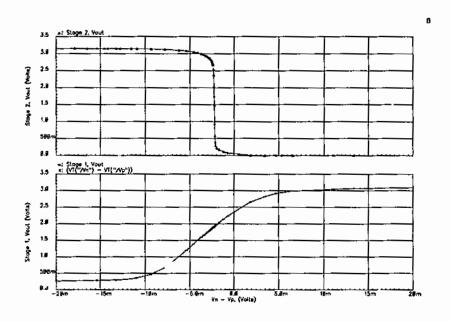

| 4.4  | Comparator simulation waveform                                       | 44 |

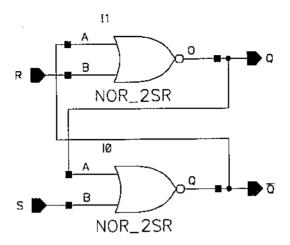

| 4.5  | SR latch schematic                                                   | 46 |

| 4.6  | SR latch simulation waveform                                         | 47 |

| 4.7  | Memory cell schematic                                                | 49 |

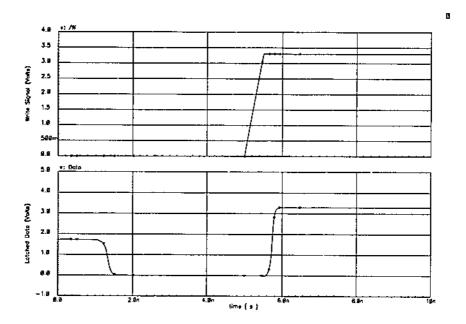

| 4.8  | Memory simulation waveform                                           | 50 |

| 4.9          | Pixel simulation waveform                                               | 52         |

|--------------|-------------------------------------------------------------------------|------------|

| 4.10         | Pixel simulation waveform, switching point enlarged                     | 52         |

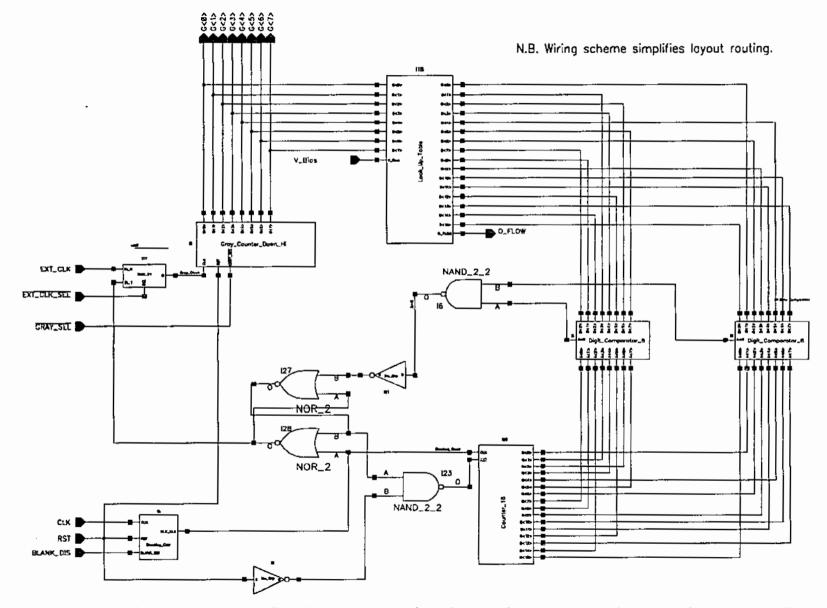

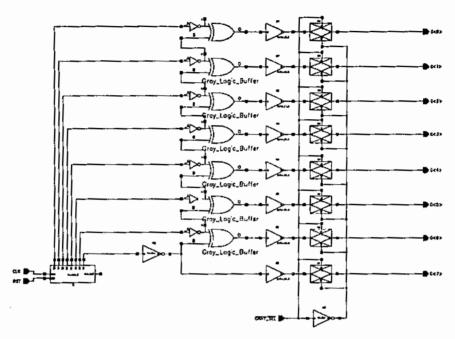

| 4.11         | Control circuit schematic.                                              | 53         |

| 4.12         | Control Circuit Block Diagram                                           | 54         |

| 4.13         | Blanking circuit schematic                                              | 54         |

| 4.14         | Gray counter schematic                                                  | 55         |

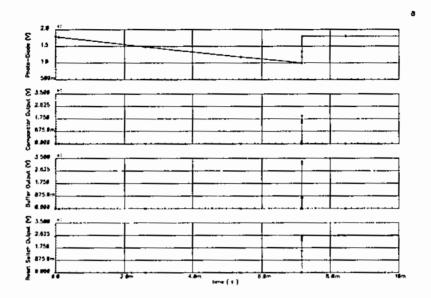

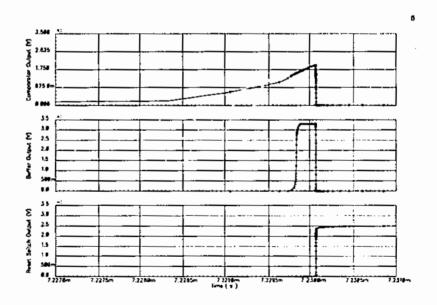

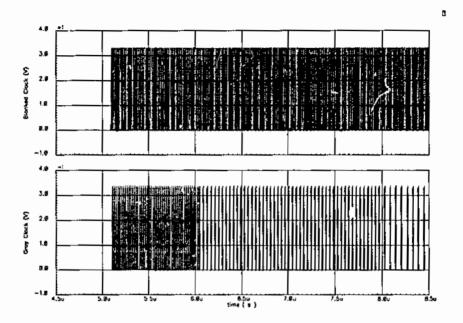

| 4.15         | Control circuit simulation waveform.                                    | 57         |

| 4.16         | Pixel and control circuit simulation waveform                           | 58         |

| 4.17         | Plot of simulation results, conversion count versus photocurrent        | 59         |

| 4.18         | Plot of simulation results, integration time versus photocurrent        | 59         |

| 4.19         | Floor-plan for the DPS array chip                                       | 60         |

| 4.20         | Fixel layout, showing dimensions and component parts                    | 62         |

| 4.21         | Photodiode, pixel, and array guard rings                                | 63         |

| 5.1          | DPS array test environment                                              | 66         |

| 5.2          | Control console                                                         | 67         |

| 5.3          | Operational block diagram.                                              | 69         |

| 5.4          | Test structure schematics                                               | 73         |

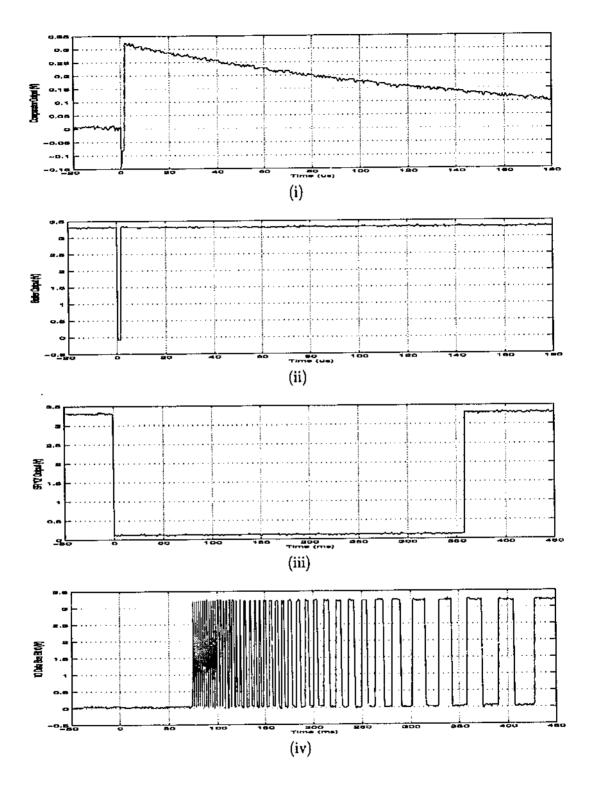

| 5.5          | Test results: control circuit functional test                           | <b>7</b> 5 |

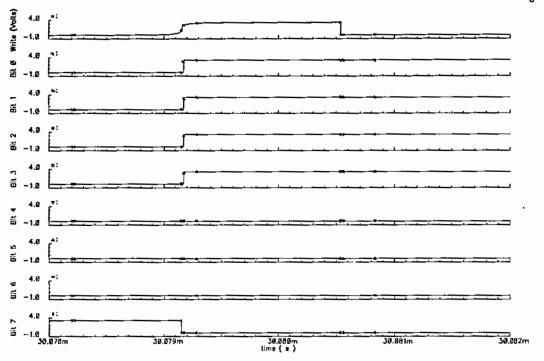

| 5.6          | Test results: test circuit outputs captured by the DSO                  | 77         |

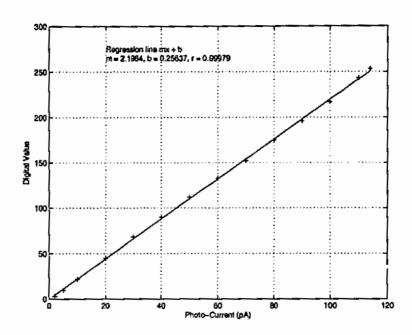

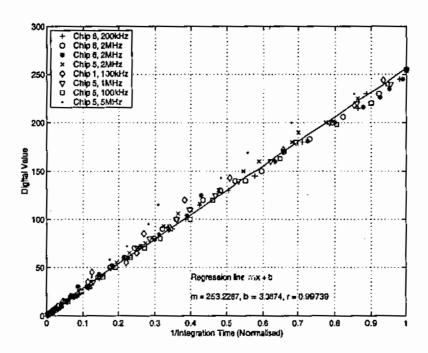

| 5.7          | Test results: digital pixel value vs 1/integration time                 | 78         |

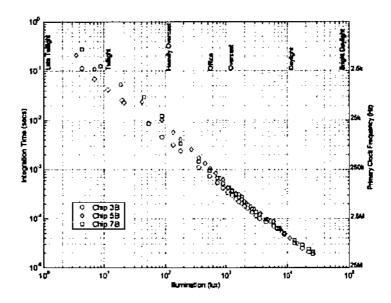

| 5.8          | Test results: integration time and primary clock frequency versus       |            |

|              | illumination                                                            | 80         |

| 5.9          | Captured image of the Australian fifty dollar note                      | 81         |

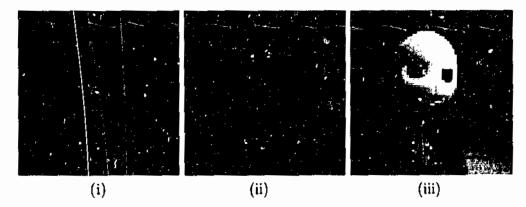

| <b>5.</b> 10 | Three images demonstrating blanking, fixed and variable clock captures. | 82         |

| 5.11         | Test results: deviation of digital pixel value from local mean          | 83         |

| 5.12         | Ten images of an office desk and window, demonstrating adaptation       | 85         |

| 5.13         | Two images of a lamp, demonstrating adaptation                          | 85         |

| 5.14         | Three images of 'Po', demonstrating a wide dynamic range capture        | 86         |

| 5.15         | Test results: spectral response of the DPS array                        | 87         |

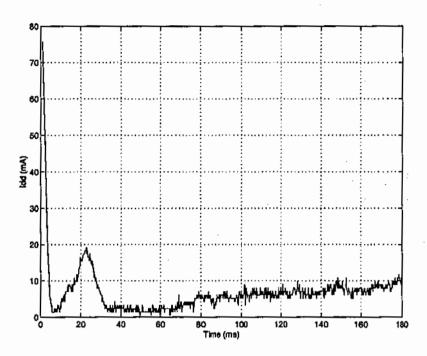

| 5.16         | Test results: quiescent analogue supply current                         | 88         |

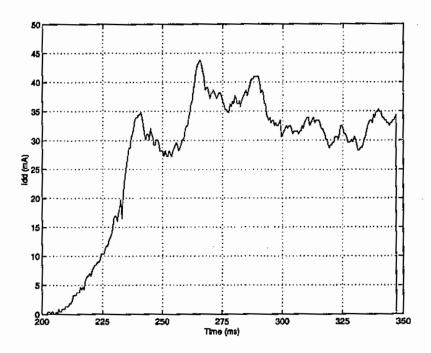

| 5.17         | Test results: plot of the digital supply current during capture         | 89         |

| 5.18         | Test results: plot of the digital supply current during readout         | 90         |

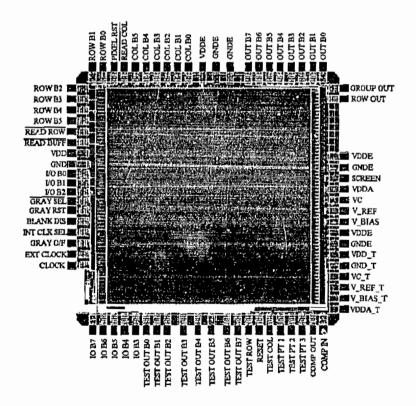

| B.1          | Bonding pad diagram                                                     | 97         |

# List of Tables

| 5.1        | DPS array power supply requirements 6                  | 7 |

|------------|--------------------------------------------------------|---|

| 5.2        | Dark current results                                   | 9 |

| 5.3        | FPN results                                            | 4 |

| 5.4        | Test results: supply and bias line quiescent current 8 | 8 |

| A.1        | Lookup table values                                    | 6 |

| B.1        | Control pin table                                      | 8 |

| <b>B.2</b> | Address pin table 9                                    | 8 |

| B.3        | Data pin table                                         | 8 |

| B.4        | Power pin table                                        | 9 |

| B.5        | Test circuit pin table                                 | 9 |

## Chapter 1

### Introduction

The capturing and processing of images has undergone a revolution in recent years. Personal computers have become commonplace, in turn creating a demand for digital cameras. While these commercial devices have increased remarkably in quality and resolution, they are primarily intended for the production of high quality images and have many drawbacks when they are applied to the task of image processing, particularly in real time. At the heart of this problem is the incompatibility of the processes used to manufacture different sections of the camera. Light sensing is generally performed by a Charge Coupled Device (CCD) array, while control, memory and processing is performed using digital Complementary Metal Oxide Semiconductor (CMOS) circuits. These systems must be manufactured separately and combined at the board level, resulting in increased production costs, and increased power consumption (an inevitable result of chip-to-chip interfacing). Aside from manufacturing problems, there are other issues relating to the inflexibility in the operation of CCD arrays that makes them less than ideal for applications requiring image processing. (These will be covered more fully in Chapter 2.)

With technology scaling resulting in CMOS devices with sub-micron feature sizes, a preferred solution is to construct the sensor array from the same CMOS technology as the control circuits, employing either Passive Pixel Sensors (PPS) or Active Pixel Sensors (APS). In this way the light sensing array is integrated with the control circuit in a single Integrated Circuit (IC) resulting in the so called 'camera on chip' [11]. The main challenge in this approach is how to convert the image

represented by analogue voltages to a digital value, while maintaining the speed, low noise, and low power consumption that this technique promises. Exploiting the reduction in feature size further, results in the *Digital Pixel Sensor* (DPS), which attempts to overcome some of the weaknesses of earlier designs by digitising the image at the pixel level. This architecture presents its own challenges, many of which are yet to be overcome.

#### 1.1 Thesis Objectives

The objective of this thesis is to develop and test a DPS sensor array, manufactured using a commercial CMOS process. The sensor is to operate over a wide range of illumination robustly, with minimal external control or timing. The digitised image is to be read from the array non-destructively, as if the array was a *Read Only Memory* (ROM) (the control circuit will not be able to write back to the array).

To this end a new implementation of single slope conversion will be presented, which employs time as the conversion variable, rather than voltage. This will allow the Analogue to Digital Conversion (ADC) process to be distributed between the control circuit and the pixels themselves. Unlike other forms of single slope conversion, the image is digitised during the exposure period, simplifying the control sequence. This also results in a digital 'electronic shutter speed' control, analogous to the shutter speed setting in a traditional camera.

#### 1.2 Thesis Organisation

Chapter 2 introduces the subject of image sensor arrays, and compares CCD and CMOS pixel sensors, highlighting the advantages of each technology. Current work on CMOS sensor arrays, and in particular DPS arrays is reviewed. Chapter 3 develops a simplified model for the semiconductor sensor element, and uses this to determine the timing and control requirements for the analogue to digital conversion scheme, which is confirmed by simulation. An architecture for the pixel and the control circuit is proposed which is suitable for realisation in digital CMOS

technology. Chapter 4 develops these architectures into working circuits, suitable for manufacture using a standard digital CMOS process. This includes both the schematic design and the hardware layout of the DPS array, and the supporting circuits required to operate it. The system is simulated to confirm the operation of the array, and the time domain ADC process. The manufactured DPS array is tested in Chapter 5, which describes the operation, the test environment, and the test procedures. Results of testing, and sample images are presented. Chapter six concludes the thesis, and discusses future work.

## Chapter 2

# Review of Digital Image Sensors

#### 2.1 Introduction

This chapter reviews the current state of image sensors, comparing the advantages of each, and how these determine their appropriate use. Terminology particular to image sensor design is also introduced, in order to address and compare important features of each approach.

### 2.2 Charge Coupled Device Sensors

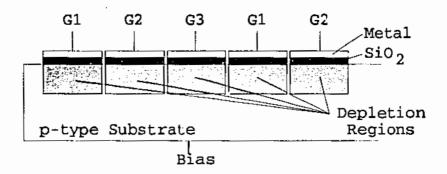

CCD sensors have been the primary technology for solid state image sensor arrays since their development in the late 1960's. Today they are the sensor of choice for high resolution (both spatial and signal) image sensors. A CCD pixel cannot be considered in isolation, and must be considered as part of a series of pixels, formed from MOS capacitors. Consider Figure 2.1 as part of a row of pixels in a CCD array, with the gates G1, G2 and G3 repeated in sequence along the row. Placing a positive voltage on a gate will deplete p-type substrate around the gate of carriers. Carriers may then be generated thermally, or through interaction with incident photons, optically within the depletion region. The positive potentials are applied to the gates as a series pulses, beginning with G1. Due to the positive potential applied to G1, any carriers that have been thermally or optically generated in the region are trapped within a 'potential well' as a 'packet' of charge. If a second positive pulse

Figure 2.1: Simplified CCD structure, showing a cross section of part of one row. In this example three clock phases are required, each being distributed in turn to the cell gates.

is then applied to the adjacent gate, G2, some of the charge from under G1 will be transferred, and shared between the two MOS capacitors. If the potential on G1 is then removed, all of the charge from the first cell will, in theory at least, transfer to the second cell. The process can then be repeated with G2 and G3, and so on. At the periphery of the array the charge is transferred to another CCD structure, perpendicular to the main array, which can then transfer the charges one 'packet' at a time to a charge amplifier, and from there to an ADC.

CCD's have evolved enormously, and the manufacturing processes for CCD's have become highly specialised. For example the p-type substrate can now be manufactured thin enough to be optically transparent, allowing the array to be 'backside' illuminated. This means that none of the array is obscured by metal contacts, and all of it can generate carriers, increasing its efficiency. As an example, Tower et al. describe a five megapixel, backside illuminated CCD array for used for space surveillance [17]. There is little doubt that CCD sensors will continue to be the technology of choice for high sensitivity, high resolution image sensors for some time.

However, from this simplistic description of the CCD operation some of its major drawbacks can be highlighted. The CCD array requires a great deal of switching, as the images must be shifted out pixel by pixel, column by column, row by row. The reading is destructive, requiring external memory to store the image. The timing, conversion and memory circuits must be fabricated on a separate IC, as the CCD

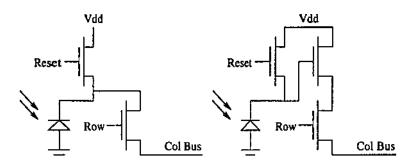

Figure 2.2: (i) Passive Pixel Sensor (PPS). (ii) Active Pixel Sensor (APS). Although shown with photodiodes, photogates can also be used in direct integration mode.

manufacturing process is unsuitable to manufacture these devices. This amount of switching activity combined with chip interfacing results in a complex control circuit, slow readout and high power consumption.

#### 2.3 Passive and Active CMOS Sensors

CMOS photo-sensors are formed either from the source/substrate junction of a CMOS transistor (a photodiode), or from the depletion region formed at the gate of the transistor (a photogate). (The structure and performance of these will be examined in detail in the next chapter.) The most common mode of operation is termed 'direct integration'. Put briefly, the reverse biased diode can be considered a system with two parallel components: a current source which is proportional to the illumination, and a capacitance formed by the p-n junction depletion region. To operate in integration mode, the cathode of the diode is first connected to a 'reset' voltage, which rapidly charges the depletion capacitance. The voltage is then disconnected, and the leakage current, which is mainly due to optically generated carriers, will discharge the capacitor linearly over time. This process 'integrates' the photocurrent over the integration period, and the voltage present at the end of the period is inversely proportional to the illumination (a high illumination results in a low voltage). This voltage is then connected to an ADC, and converted to a digital value. In a (PPS) such as that of Figure 2.2(i), the photodiode is connected

to a charge amplifier, via a row selection transistor and a column bus line, and from there to the input of an ADC. In any CMOS circuit long bus lines represent a large capacitive load, and connecting the sensor results in charge sharing, and significant signal attenuation. To alleviate these effects the APS includes a single voltage follower in each pixel as per Figure 2.2(ii), to increase the ability to drive the bus impedance [11]. Sufficient time must still be allowed for the small voltage follower buffer to charge the large capacitance of the column select line. This is the limiting factor for the image acquisition rate.

#### 2.3.1 Analogue to Digital Conversion

In any solid state array the main challenge is how to convert the analogue signal level present at the sensing element to a digital value, or how to route the sensor to the ADC. The ADC method employed in a CMOS or CCD sensor array depends upon the application and the architecture of the array. An array level ADC (the ADC is shared by the entire array) must digitise one pixel signal at a time, and to maintain a reasonable readout speed, is typically of the flash or half-flash type. These consume large silicon areas, and an acceptable trade off is to provide an ADC of a slower, and physically smaller design, at the column level.

#### 2.3.2 Fixed Pattern Noise

Regardless of the pixel or array design, all CMOS image sensors suffer from Fixed Pattern Noise (FPN). Each device created on an integrated circuit has certain characteristics that determine its performance, such as its threshold voltage or terminal capacitance. A commercial CMOS manufacturing process allows for a range of device characteristics which are considered acceptable. These are typically within 2 to 3 standard deviations of the mean, assuming a normal distribution of device parameters [19]. Steps can be taken to minimise the impact of this 'process variation' on the performance of the pixel array, in particular one technique called Correlated Double Sampling (CDS). In this technique, the pixel voltage is sampled immediately after reset, and the value stored in a MOS capacitor (at the column level). After the

integration period the pixel voltage is again sampled and the difference between the two signal levels is digitised. This effectively reduces offset FPN due to variations the column selection and buffering circuits, but cannot remove multiplicative FPN due to amplifier gain [11] [7] [5].

#### 2.3.3 Temporal Noise

There are three main sources of temporal noise in a CMOS sensor: shot, thermal and  $\frac{1}{I}$  noise. A detailed analysis of these noise sources is beyond the scope of this review, suffice it to say that temporal noise determines the low illumination limit of the sensor [16]. In addition to the noise present in the photo-detector any additional circuitry (such as reset, follower and selection transistors) will also introduce noise. Considering only the photodiode itself, shot noise is the most significant noise source. CDS can also alleviate some temporal noise sources (thermal, reset and  $\frac{1}{I}$ ) [11] [5].

#### 2.3.4 Fill Factor

As additional circuitry is included within the pixel, less and less of the sensor area is devoted to capturing light, which is after all the main purpose of the array. The *Fill Factor* (FF) is the ratio of the light sensitive area to the total area of the pixel, or in some cases, of the array. As stated in the previous section, modern CCD sensors achieve a fill factor of 100%. CMOS PPS sensor arrays sacrifice light sensitive area to selection transistors, power and signal lines, and achieve typically 60 to 70% FF. APS arrays, having the additional buffer transistor, generally achieve 50 to 60% FF.

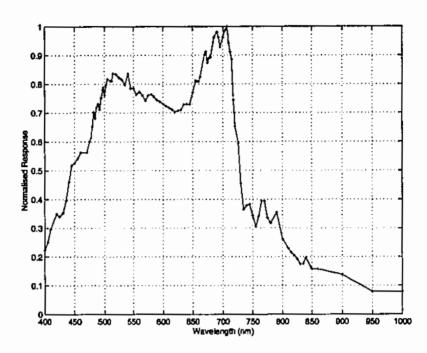

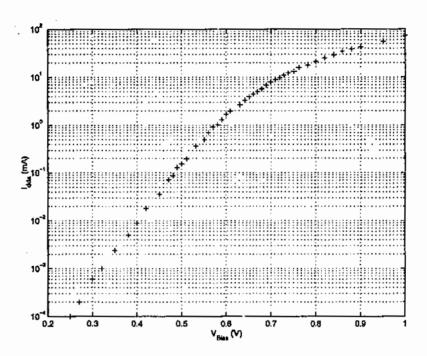

#### 2.3.5 Spatial Resolution