# **Edith Cowan University**

# **Research Online**

ECU Publications Pre. 2011

2005

# **Dynamic Spot Generation Using Opto-VLSI Processing**

Zhenglin Wang Edith Cowan University

Rong Zheng Edith Cowan University

Kamal Alameh Edith Cowan University

Follow this and additional works at: https://ro.ecu.edu.au/ecuworks

Part of the Engineering Commons

This is an Author's Accepted Manuscript of: Wang, Z., Zheng, R., & Alameh, K. (2005). Dynamic Spot Generation Using Opto-VLSI Processing. Proceedings of IFIP WG 10.5 International Conference on Very Large Scale Integration System-on-Chip. (pp. 288-290). Perth. IFIP. Available here. This Conference Proceeding is posted at Research Online.

https://ro.ecu.edu.au/ecuworks/2951

# Dynamic Spot Generation Using Opto-VLSI Processing

Zhenglin Wang, Rong Zheng, and Kamal E. Alameh Centre for Microphotonic Systems, Electron Science Research Institute, Edith Cowan University, Joondalup, WA, 6027, Australia.

Email: z.wang@ecu.edu.au

#### Abstract:

In this paper we demonstrate the capability of Opto-VLSI processors to generate arbitrary optical power distribution for adaptive optical beam splitting and dynamic optical spot generation. By using the multicasting capability of Opto-VLSI processors, an input optical signal can be dynamically split into N spots array, and the output power of each spot can be independently configured. Experimental results of multiple beam splitting show that dynamic optical multicasting can be achieved with more than 20dB dynamic range. Special patterns are also generated by optimising the phase hologram of the Opto-VLSI processor to place the output beam spots at appropriate positions.

#### 1. Introduction:

Diffractive optical elements that multicast single laser source are essential components for dynamic optical access network and reconfigurable parallel computing architectures. In these systems, great advantages can be gained if the intensity of the input beam is dynamically split according to a reconfigured weight matrix [1, 2].

Many passive and active structures have been developed to realise dynamic optical splitting [3-7]. While passive optical splitters are adequate for current optical access networks, future services require reconfigurable optical splitters because they overcome the major flexibility limitation of static optical splitters encountered in existing optical networks. In a dynamic mode, a reconfigurable optical splitter can dynamically distribute the optical power without changing its physical configuration. This offers a more flexible and cost-effective option in comparison to passive optical splitters. A smooth migration from passive to totally dynamic optical splitters is therefore necessary for future reconfigurable optical networks [8].

Opto-VLSI processors have recently demonstrated for realising dynamic optical power distribution [9]. An Opto-VLSI processor is an optical spatial phase modulator capable of achieving beam steering, focusing and multicasting. A typical Opto-VLSI processor consists of liquid crystal (LC) pixels driven by a Very-Large-Scale-Integrated (VLSI) circuit. each pixel can be driven by many discrete voltage levels thus generating phase holograms capable of performing adaptive optical beam steering/multicasting through quantized phase holograms uploaded onto the Opto-VLSI processor.

In this paper, we demonstrate the capability of Opto-VLSI processors to generate dynamic optical power splitting profiles. Improved simulated annealing (SA) algorithm is used to calculate the phase holograms that generate arbitrary output splitting profiles. Experiments are setup to generate proof-of-concept 1x3, 2x3, and 3x3 spots arrays. Output optical beams are coupled into output fibre ports by a piecewise linear optic to monitor output properties. Experimental results show more than 20dB dynamic range and good power distribution accuracy. Different spot arrays are generated at appropriate positions to form alphabet letters, which demonstrate the capability Opto-VLSI processors to synthesise arbitrary spot patterns.

#### 2. Improved Simulated Annealing Algorithm

The Opto-VLSI processor is driven by computer holograms generated using a simulated annealing (SA) algorithm [10], which first defines a cost function as a measure of the distance between the diffracted field pattern of a target output spot array and the field pattern of the current candidate hologram. The algorithm starts from an initial random hologram pattern, h(x,y), and computes the resulting diffraction field represented by a Fourier transform. For a pixellated hologram, h(m,n). the diffracted beam H(k,l) is described by

$$H(k,l) \equiv DFT\{h(m,n)\} \tag{1}$$

where DFT denotes the discrete Fourier Transform. and (m,n) and (k,l) represent the coordinates in the hologram and output planes, respectively. A cost function is calculated as a measure of the discrepancy between the target spot array and the diffraction field of the hologram. Next, a pixel or a group of pixels are randomly changed (subject to the constraint on the phase levels), then the cost function is calculated again. Note that there is no need to recalculate the entire diffraction field H(k,l), when changing a pixel; it will be possible to compute the change in diffraction field  $\Delta H_T$ arising from the change in a single pixel  $\Delta h_{m,n}$  as follows

$$\Delta H_T = \Delta h_{m,n} e^{-2\pi j(km + \ln l)/N}$$

(2)

This results in a change in cost function,  $\Delta C$ . If the cost decreases (that is  $\Delta C$  is negative), the pixel change is accepted, otherwise, the pixel is accepted with a probability of  $e^{\Delta C/T}$ , where T is the "temperature", which is gradually reduced as the number of iterations

increases. The evolution of the temperature as a function of the number of iterations is expressed as

$$T = T_o e^{-T_c i/I}$$

(3)

where  $T_v$  and  $T_v$  are parameters that determine the starting value and rate of decrease of the temperature, i is the current iteration number, and I is the total number of desired iterations. The end of the algorithm can be set at a certain number of iterations, or when the cost has been reduced to a determined level, or alternatively, when the temperature has been reduced to a certain value.

To reduce the time required for hologram generation and channel crosstalk, and most importantly to improve diffraction efficiency, we modified the algorithm by adding constraints on active pixel number (m,n) that only the pixels that encircle the diameter of the incident beam are used for hologram calculation, whereas all other pixels are masked with their phases set to zeros.

## 3. Experiment setup

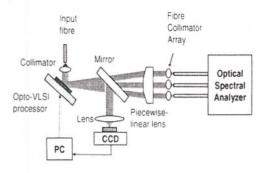

In our experiments, a 40-micron pixel size, 128x128pixel nematic LC Opto-VLSI processor was used and the input Gaussian optical beam was collimated to a beam diameter of 1mm so that the number of active pixel encircling the input optical beam was 50x50 (rather than the whole 128x128-pixel area of the Opto-VLSI processor), which has 2x2 mm<sup>2</sup> active area and covers more than 99% of the input optical power. The basic structure of the dynamic optical power splitter using Opto-VLSI technology is shown in Figure 1. It comprises an input fibre collimator, an Opto-VLSI processor, a three channel piecewise linear prism as an optical router, and an output fibre collimator array. The input optical signal is transformed, via the input collimating lens, into free-space collimated Gaussian optical beam with beam diameter about 1mm, which illuminates a 50×50-pixel block on the Opto-VLSI processor. The 50×50-pixel block is driven by a multicasting holographic diffraction grating, which is calculated based on the improved SA algorithm using MATLAB programs. The output spot patterns were directly captured by a CCD camera through a sampling mirror, and analysed by a Spiricon beam profile analyser. To couple the output beams into fibre ports, a fibre collimator array was used and connected to an Optical Spectrum Analyser (OSA) for power measurements. The role of the piecewise linear lens was to steer the diffracted split beams along parallel directions so that they can be coupled into the output fibre collimator array with high efficiency.

Fig.1 Experimental setup of dynamic power splitter using an Opto-VLSI processor

## 4. Experimental results:

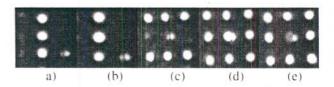

A variety of holograms were generated to control the Opto-VLSI processor and demonstrate its capability to realize dynamic power splitting. Figure 2 shows the measured output spot arrays for an input optical beam that was dynamically split into (a) three uniform output spots with equal output power. (b) three spot array with one spot output power down to a half and the other spot powers kept unchanged (the beam spot to the right is the diffracted zeroth order beam, which has low power compared to the other output spots), (c) 2x3 spot array with uniform power distribution, (d) 3x3 spots array with uniform power distribution, and (e) 3x3 spots array with the centre beam removed. It is obvious from Figs 2(a)-(e) that the zeroth order beams have low power compared to the split spots, and are located at different positions than the split beams by properly defining their positions, hence they are not coupled into the output fibre ports. It is worthwhile noting that the position and power of each output spot can independently be adjusted by generating optimized phase holograms that produces the desired spot profiles.

Fig.2 Dynamic spot array generation using Opto-VLSI processor.

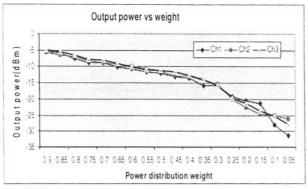

Figure 3 shows the measured output power versus the normalized target power per channel for a three-channel splitter. A very good splitting uniformity is seen for normalized splitting ratios higher than 0.2. For lower splitting ratios, the splitting uniformity is slightly degraded due to the fact that the crosstalk becomes higher than the power of the split spots.

Fig.3 Measured three channel output power verses power distribution weight

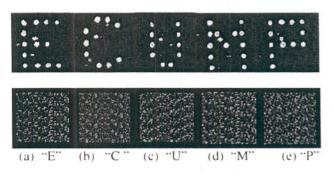

By appropriately defining the output spot powers and spot positions, some special patterns can be generated at the output plane. Figure 4 shows the phase holograms and the corresponding patterns, which are the capital letters "E" "C" "U" "M" "P". It is obvious that arbitrary patterns can be generated using the simulated annealing algorithm.

Figure 4 Holograms generating different capital letters.

#### 5. Conclusion:

A dynamic optical power splitter based on a reconfigurable Opto-VLSI processor is presented in this paper. It can be used as an active beam splitter or special spot pattern generator. An improved simulated annealing algorithm is used to calculate the phase holograms using MATLAB Software, which enabled a much shorter programming time and a higher diffraction efficiency to be attained. Proof-of-concept reconfigurable 1:3 optical splitter that utilizes an Opto-VLSI processor to adaptively split optical signal into different output fibre ports has experimentally been demonstrated, and the results show more than 20dB dynamic range. Different output spots including alphabet letters with arbitrary weights at arbitrary positions have also been generated demonstrating the 'capability of Opto-VLSI processors to realise dynamic power multicasting. .

#### Acknowledgement

This project is support by Australian Research Council (ARC) and The Office of Science and Innovation, Western Australian Government.

### Reference

- 1.F. Ratovelomanana, N. Vodjdani, A. Enard, G. Glastre, D. Rondi, and R. Blondeau, "Active lossless monolithic one-by-four splitters/combiners using optical gates on InP," *IEEE Photon. Technol. Lett.*, vol. 7, pp. 511–513, 1995.

- U. Koren, M. G. Young, B. I. Miller, M. A. Newkirk, M. Chien, M. Zirngibl, C. Dragone, B. Glance, T. L. Koch, B. Tell, K. Brown-Goebeler, and G. Raybon, "1 x 16 photonic switch operating at 1.55 um wavelength based on optical amplifiers and a passive optical splitter," *Appl. Phys. Lett.*, vol. 61, pp. 1613–1615, 1992.

- 3. J. M. Heaton, R. M. Jenkins, D. R. Wight, J. T. Parker, J. C. H. Birbeck, and K. P. Hilton, "Novel 1-to-N way integrated optical beam splitters using symmetric mode mixing in GaAs/AlGaAs multimode waveguides," *Appl. Phys. Lett.*, vol. 61, pp. 1754– 1756, 1992.

- H. Takahashi, K. Okamoto, and Y. Ohmori. "Integrated-optic 1x128 power splitter with multifunnel waveguide," *IEEE Photon. Technol. Lett.*, vol. 5, pp. 58–60, 1993.

- Choi, S.S. and Donnelly, J.P. and Groves, S.H. and Reeder, R.E. and Bailey, R.J. and Taylor, P.J. and Napoleone. A. and Goodhue. W.D.. "All-active InGaAsP-InP optical tapered-amplifier 1×N power splitters." *IEEE J. Photonics Technology Lett.* 12, pp. 974–976, 2000.

- Yves Jaouen, Laurent du Mouza, Denis Barbier, Jean-Marc Delavaux, and Piero Bruno, "Eight-Wavelength ErYb Doped Amplifier: Combiner/Splitter Planar Integrated Module," *IEEE J. Photonics Technology* Lett. 9, pp. 1105–1107, 1999.

- Ratovelomanana, F. and Vodjdani, N. and Enard, A. and Glastre, G. and Rondi, D. and Blondeau, R. "Active lossless monolithic one-by-four splitters/combiners using optical gates on InP." *IEEE J. Photonics Technology Lett.* 7, pp. 511–513, 1995.

- 8. Abe Queller. "Dynamic power distribution in PON/FTTP networks," In *Light Wave Magazine*. No. 7, pp. 29–31, 2004.

- R.Zheng, Z.Wang, K.E.Alameh and W.A.Crossland. "An Opto-VLSI Reconfigureable Broad-Band Optical Splitter". *IEEE J. Photonics Technology Lett.* 17. pp 339-341, 2005.

- 10. M.P. Dames, R.J. Dowling, P. McKnee, and D. Wood. Efficient optical elements to generate intensity weighted spot arrays: design and fabrication. *Applied Optics*, 30(19):2685–2691, July 1991